1. TUJUAN [KEMBALI]

penulisan blog ini bertujuan untuk :

· Dapat membuat dan mensimulasikan spesial output gates.

· Dapat memahami teori dan prinsip kerja dari spesial output gates.

2. ALAT DAN BAHAN [KEMBALI]

ALAT :

1. Power Supply

2. Osiloskop

BAHAN :

1. Resistor

Komponen Input :

Komponen Output :

Komponen Lainnya :

3. DASAR TEORI [KEMBALI]

- Ringkasan

5.5 CMOS Logic Family

Keluarga logika CMOS (Complementary Metal Oxide Semiconductor) menggunakan tipe-N dan tipe-P. MOSFET (peningkatan MOSFET, lebih tepatnya) untuk mewujudkan fungsi logika yang berbeda. Itu dua jenis MOSFET dirancang untuk memiliki karakteristik yang cocok. Artinya, mereka menunjukkan hal yang identik karakteristik dalam kondisi switch-OFF dan switch-ON. Keuntungan utama dari CMOS Logic Family atas logika bipolar yang dibahas keluarga sejauh ini terletak pada disipasi daya yang sangat rendah, yaitu mendekati nol dalam kondisi statis. Faktanya, perangkat CMOS mengambil daya hanya saat mereka beralih. Ini memungkinkan integrasi jumlah gerbang CMOS yang jauh lebih besar pada sebuah chip daripada yang mungkin dilakukan dengan teknologi bipolar atau NMOS.

5.5.1 Implementasi Sirkuit Fungsi Logika

5.5.1.1 Inverter CMOS

Inverter adalah blok bangunan paling mendasar dari logika CMOS. Ini terdiri dari sepasang saluran-N dan MOSFET saluran-P yang dihubungkan dalam konfigurasi kaskade seperti yang ditunjukkan pada Gambar 5.34. Rangkaian tersebut berfungsi sebagai berikut. Ketika input dalam status TINGGI (logika '1'), MOSFET saluran-P Q1 masuk keadaan cut-off saat N-channel MOSFET Q2 berjalan. MOSFET melakukan menyediakan jalur dari ground ke keluaran dan keluarannya adalah RENDAH (logika '0'). Saat input dalam status RENDAH (logika '0'), Q1 dalam konduksi sedangkan Q2 dalam cut-off. Perangkat saluran-P yang melakukan menyediakan jalur agar VDD muncul di keluaran, sehingga keluarannya dalam status TINGGI atau logika '1'.

5.5.1.2 Gerbang NAND

Gambar 5.35 menunjukkan implementasi rangkaian dasar dari NAND dua masukan. Seperti yang ditunjukkan pada gambar, dua MOSFET saluran-P (Q1 dan Q2) dihubungkan secara paralel antara VDD dan terminal keluaran, dan dua MOSFET saluran-N (Q3 dan Q4) dihubungkan secara seri antara terminal ground dan output. Sirkuit beroperasi sebagai berikut. Agar keluaran berada dalam status logika '0', penting bahwa kedua perangkat saluran-N yang terhubung seri bekerja dan kedua perangkat saluran-P yang terhubung paralel tetap ada dalam keadaan terputus. Ini hanya mungkin jika kedua input berada dalam status logika '1'. Ini memverifikasi salah satu entri tabel kebenaran gerbang NAND. Jika kedua input berada dalam status logika '0', keduanya Perangkat saluran-N adalah non-konduktor dan kedua perangkat saluran-P konduktor, yang menghasilkan logika '1' pada keluaran. Ini memverifikasi entri lain dari tabel kebenaran NAND. Untuk dua sisanya kombinasi input, salah satu dari dua perangkat saluran-N akan menjadi non-konduktor dan salah satu dari keduanya perangkat saluran-P yang terhubung secara paralel akan konduktor.

Gambar 5.36 menunjukkan caranya sirkuit pada Gambar 5.35 dapat diperpanjang untuk membangun gerbang NAND tiga masukan. Pengoperasian sirkuit ini dapat dijelaskan pada baris serupa. Dapat disebutkan di sini bahwa koneksi seri MOSFET ditambahkan ke penundaan propagasi, yang lebih besar dalam kasus perangkat saluran-P daripada dalam kasus Perangkat saluran-N. Hasilnya, konsep penambahan jumlah input seperti yang ditunjukkan pada Gambar 5.36 biasanya dibatasi pada empat input dalam kasus NAND dan tiga input dalam kasus NOR. Itu angka satu kurang dalam kasus NOR karena menggunakan perangkat saluran-P yang terhubung seri.

5.5.1.3 Gerbang NOR

Gambar 5.37 menunjukkan implementasi rangkaian dasar dari NOR dua masukan. Seperti yang ditunjukkan pada gambar, dua MOSFET saluran-P (Q1 dan Q2) dihubungkan secara seri antara VDD dan terminal keluaran, dan dua MOSFET saluran-N (Q3 dan Q4) dihubungkan secara paralel antara terminal ground dan output. Sirkuit beroperasi sebagai berikut. Agar keluaran berada dalam status logika '1', penting bahwa kedua perangkat saluran-P yang terhubung seri berjalan dan kedua perangkat saluran-N yang terhubung paralel tetap ada dalam keadaan terputus. Ini hanya mungkin jika kedua input berada dalam status logika '0'. Ini memverifikasi salah satu entri dari tabel kebenaran gerbang NOR. Jika kedua input berada dalam status logika '1', keduanya Perangkat saluran-N konduktor dan kedua perangkat saluran-P non-konduktor, yang menghasilkan logika '0' pada keluaran. Ini memverifikasi entri lain dari tabel kebenaran NOR. Untuk dua sisanya kombinasi input, salah satu dari dua perangkat saluran-N paralel akan konduktor dan salah satu dari dua perangkat saluran-P yang terhubung seri akan non-konduktor. Kami memiliki Q1 OFF dan Q3 ON atau Q2 OFF dan Q4 ON. Keluaran dalam kedua kasus adalah logika '0', yang memverifikasi entri yang tersisa dari tabel kebenaran.

Gambar 5.38 menunjukkan bagaimana rangkaian Gambar 5.37 dapat diperpanjang untuk membangun gerbang NOR tiga masukan. Pengoperasian rangkaian ini dapat dijelaskan pada jalur serupa. Seperti yang sudah dijelaskan, gerbang NOR dengan lebih dari tiga input biasanya direalisasikan sebagai kombinasi gerbang yang lebih sederhana.

5.5.1.4 Gerbang AND

Gerbang AND tidak lain adalah gerbang NAND yang diikuti oleh inverter. Gambar 5.39 menunjukkan internal skema dari dua masukan AND di CMOS. Gerbang AND yang disangga dibuat dengan menggunakan gerbang NOR skema dengan inverter di kedua input dan outputnya memberi makan dua inverter yang terhubung seri.

5.5.1.5 Gerbang OR

Gerbang OR tidak lain adalah gerbang NOR diikuti oleh inverter. Gambar 5.40 menunjukkan internal skema dari dua input OR di CMOS. Gerbang OR buffered dibuat dengan menggunakan gerbang NAND skema dengan inverter di kedua input dan outputnya memberi makan dua inverter yang terhubung seri.

5.5.1.6 Gerbang EKSKLUSIF-OR

Gerbang EKSKLUSIF-OR diimplementasikan menggunakan diagram logika pada Gambar 5.41 (a). Seperti yang terlihat dari gambar, output dari pengaturan logika ini dapat diekspresikan oleh

Gambar 5.41 (b) menunjukkan skema internal dari gerbang EX-OR dua masukan. MOSFET Q1 – Q4 merupakan gerbang NOR. MOSFET Q5 dan Q6 mensimulasikan ANDing dari A dan B, dan MOSFET Q7 menyediakan ORing dari output NOR dengan output ANDed. Sejak MOSFET Q8 – Q10 make up melengkapi susunan MOSFET Q5 – Q7, hasil akhirnya dibalik. Jadi, Skema Gambar 5.41 (b) mengimplementasikan susunan logika dari Gambar 5.41 (a) dan karenanya dua masukan Gerbang EX-OR.

5.5.1.7 Gerbang EKSKLUSIF-NOR

Gerbang EXCLUSIVE-NOR diimplementasikan menggunakan diagram logika pada Gambar 5.42 (a). Seperti yang terbukti dari gambar tersebut, keluaran dari susunan logika ini dapat diekspresikan dengan

Gambar 5.42 (b) menunjukkan skema internal dari gerbang EX-NOR dua masukan. MOSFET Q1 – Q4 merupakan gerbang NAND. MOSFET Q5 dan Q6 mensimulasikan ORing dari A dan B, dan MOSFET Q7 menyediakan ANDing dari keluaran NAND dengan keluaran ORed. Sejak MOSFET Q8 – Q10 melengkapi susunan MOSFET Q5 – Q7, hasil akhirnya dibalik. Jadi, skema Gambar 5.42 (b) mengimplementasikan susunan logika dari Gambar 5.42 (a) dan karenanya dua masukan Gerbang EX-NOR.

5.5.1.8 Gerbang AND-OR-INVERT dan OR-AND-INVERT

Gambar 5.43 menunjukkan skema internal dari gerbang AND-OR-INVERT dua-lebar, dua-masukan. Output dari gerbang ini dapat diekspresikan secara logis dengan persamaan Boolean

Gambar 5.44 menunjukkan tipikal skema internal gerbang dua-lebar, dua-masukan OR-DAN-INVERT. Output dari gerbang ini bisa jadi diekspresikan dengan persamaan Boolean

Sangat mudah untuk menggambar skema internal gerbang AND-OR-INVERT atau OR-AND-INVERT. Rangkaian ini memiliki dua bagian, yaitu bagian MOSFET saluran-N dari rangkaian dan bagian saluran-P dari sirkuit. Mari kita lihat, misalnya, bagaimana persamaan Boolean (5.4) berhubungan dengan rangkaian Gambar 5.44.

Fakta yang kita butuhkan (A OR B) AND (C OR D) menjelaskan mengapa MOSFET N-channel mewakili Input A dan B adalah paralel dan juga mengapa MOSFET N-channel mewakili C dan D juga secara paralel. Kedua susunan paralel tersebut kemudian dihubungkan secara seri untuk mencapai sebuah ANDing operasi. Bagian MOSFET saluran-P pelengkap mencapai inversi. Perhatikan bahwa P-channel Bagian adalah pelengkap dari bagian saluran-N dengan MOSFET saluran-N diganti dengan saluran-P MOSFET dan koneksi paralel diganti dengan koneksi seri, dan sebaliknya. Pengoperasian file Gerbang AND-OR-INVERT dapat dijelaskan pada baris yang mirip dengan kasus gerbang OR-AND-INVERT.

5.5.1.9 Gerbang Transmisi

Gerbang transmisi, juga disebut sakelar bilateral, eksklusif untuk logika CMOS dan tidak memiliki mitra dalam keluarga TTL dan ECL. Ini pada dasarnya adalah sakelar satu kutub, satu lemparan (SPST). Operasi pembukaan dan penutupan dapat dikontrol oleh level logika yang diterapkan secara eksternal. Gambar 5.45 (a) menunjukkan simbol sirkuit. Jika logika '0' pada input kontrol sesuai dengan sakelar terbuka, maka a logika '1' sesuai dengan sakelar tertutup, dan sebaliknya.

Skema internal gerbang transmisi tidak lain adalah koneksi paralel dari N-channel MOSFET dan P-channel MOSFET dengan input kontrol diterapkan ke gerbang, seperti yang ditunjukkan pada Gambar. 5.45 (b). Kontrol input ke terminal gerbang dua MOSFET adalah pelengkap satu sama lain. Ini dipastikan dengan inverter bawaan. Ketika input kontrol TINGGI (logika '1'), kedua perangkat berjalan dan sakelar ditutup. Ketika input kontrol adalah RENDAH (logika '0'), kedua perangkat terbuka dan oleh karena itu sakelar terbuka.

5.5.1.10 CMOS dengan Output Pembuangan Terbuka

Output dari gerbang CMOS konvensional tidak boleh disingkat bersama-sama, seperti yang diilustrasikan pada kasus dua inverter mengalami korsleting di terminal keluaran (Gbr. 5.46). Jika kondisi input sedemikian rupa sehingga outputnya salah satu inverter TINGGI dan yang lainnya RENDAH, rangkaian keluaran kemudian seperti pembagi tegangan jaringan dengan dua resistor identik yang sama dengan resistansi ON dari MOSFET konduksi. Outputnya adalah kemudian kira-kira sama dengan VDD / 2, yang terletak pada kisaran tak tentu dan oleh karena itu tidak dapat diterima. Selain itu, pengaturan seperti ini menarik arus berlebih dan dapat menyebabkan kerusakan perangkat.

Masalah ini tidak ada di gerbang CMOS dengan keluaran saluran terbuka. Perangkat semacam itu adalah rekannya ke gerbang dengan keluaran kolektor terbuka dalam keluarga TTL. Tahap keluaran dari gerbang CMOS dengan open keluaran saluran adalah MOSFET saluran-N tunggal dengan terminal saluran terbuka, dan tidak ada saluran-P MOSFET. Terminal drainase terbuka perlu dihubungkan ke VDD melalui resistor pull-up eksternal. Gambar 5.47 menunjukkan skema internal CMOS inverter dengan keluaran saluran terbuka. Penarikan resistor yang ditampilkan di sirkuit eksternal ke perangkat.

5.5.1.11 CMOS dengan Output Tristate

Seperti TTL tristate, perangkat CMOS juga tersedia dengan output tristate. Pengoperasian tristate Perangkat CMOS mirip dengan yang ada pada TTL tristate. Artinya, saat perangkat diaktifkan, ia menjalankannya fungsi logika yang dimaksudkan, dan ketika dinonaktifkan outputnya beralih ke status impedansi tinggi. Dalam keadaan impedansi tinggi, baik MOSFET saluran-N dan saluran-P didorong ke keadaan-OFF. Gambar 5.48 menunjukkan skema internal buffer tristate dengan input LOW ENABLE aktif. Sirkuit ditampilkan adalah salah satu buffer di buffer CMOS hex jenis CD4503B. Output dari perangkat CMOS tristate dapat dihubungkan bersama dalam susunan bus, seperti perangkat TTL tristate dengan kondisi yang sama itu hanya satu perangkat yang diaktifkan pada satu waktu.

5.5.1.12 Input Mengambang atau Tidak Digunakan

Input yang tidak digunakan dari perangkat CMOS tidak boleh dibiarkan mengambang atau tidak terhubung. Input mengambang sangat tinggi rentan terhadap kebisingan dan akumulasi muatan statis. Hal ini seringkali dapat menyebabkan simultan konduksi perangkat saluran-P dan saluran-N pada chip, yang menyebabkan peningkatan disipasi daya dan kepanasan. Input yang tidak digunakan dari gerbang CMOS harus dihubungkan ke ground atau VDD atau disingkat ke masukan lain. Hal yang sama berlaku untuk input dari semua gerbang yang tidak digunakan. Sebagai contoh, kita mungkin hanya menggunakan dua dari empat gerbang yang tersedia pada IC yang memiliki empat gerbang. Masukan dari dua gerbang yang tersisa harus diikat ke ground atau VDD.

5.5.1.13 Perlindungan Input

Karena impedansi input yang tinggi pada perangkat CMOS, perangkat ini sangat rentan terhadap muatan statis membangun. Sebagai akibatnya, tegangan yang dikembangkan melintasi terminal input bisa menjadi cukup tinggi menyebabkan kerusakan dielektrik lapisan oksida gerbang. Untuk melindungi perangkat dari ini muatan statis build-up dan konsekuensi merusaknya, input perangkat CMOS dilindungi menggunakan jaringan resistor-dioda yang sesuai, seperti yang ditunjukkan pada Gambar 5.49 (a). Sirkuit proteksi yang ditunjukkan biasanya digunakan dalam MOSFET gerbang logam seperti yang digunakan pada perangkat CMOS 4000-series.

Dioda D2 membatasi lonjakan tegangan positif ke VDD + 0,7 V, sedangkan dioda D3 menjepit lonjakan tegangan negatif hingga −0,7 V. Resistor R1 membatasi amplitudo arus lucutan statis dan dengan demikian mencegah kerusakan tegangan besar dari yang langsung diterapkan ke terminal input. Diode D1 tidak berkontribusi pada input perlindungan. Ini adalah persimpangan P – N terdistribusi yang ada karena proses difusi yang digunakan untuk fabrikasi dari resistor R1. Dioda proteksi tetap bias terbalik untuk kisaran tegangan input normal 0 hingga VDD, dan oleh karena itu tidak mempengaruhi pengoperasian normal.

Gambar 5.49 (b) menunjukkan sirkuit proteksi input tipikal yang digunakan untuk MOSFET gerbang silikon yang digunakan dalam 74C, 74HC, dll., Perangkat CMOS seri. Persimpangan P – N terdistribusi tidak ada karena R1 merupakan polisilikon penghambat. Dioda D1 dan D2 melakukan pekerjaan yang sama seperti dioda D2 dan D3 dalam kasus perangkat gerbang logam. Dioda D2 biasanya dibuat dalam bentuk transistor bipolar dengan terminal kolektor dan basisnya dihubung singkat.

5.5.1.14 Kondisi Latch-up

Ini adalah kondisi yang tidak diinginkan yang dapat terjadi pada perangkat CMOS karena adanya parasit transistor bipolar (NPN dan PNP) tertanam di substrat. Sementara MOSFET N-channel mengarah ke keberadaan transistor NPN, MOSFET saluran-P bertanggung jawab atas keberadaan transistor PNP. Jika kita melihat pengaturan daerah semikonduktor yang berbeda di gedung CMOS yang paling dasar blok, yaitu inverter, kita akan menemukan bahwa transistor NPN dan PNP parasit ini menemukan dirinya sendiri saling berhubungan dalam pengaturan back-to-back, dengan kolektor satu transistor terhubung ke basis dari yang lain, dan sebaliknya. Dua pasang transistor yang dihubungkan secara seri ada antara VDD dan ground dalam kasus inverter, seperti yang ditunjukkan pada Gambar. 5.50. Jika karena alasan tertentu elemen parasit ini dipicu ke konduksi, karena umpan balik positif yang melekat, mereka masuk ke kondisi latch-up dan tetap dalam konduksi secara permanen. Hal ini dapat menyebabkan aliran arus besar dan selanjutnya untuk menghancurkan perangkat. Kondisi latch-up dapat dipicu oleh lonjakan tegangan tinggi dan dering hadir di input dan output perangkat. Perangkat juga rentan terhadap latch-up jika maksimal peringkat terlampaui. Perangkat CMOS modern menggunakan teknik fabrikasi yang ditingkatkan untuk meminimalkan faktor-faktor yang dapat menyebabkan efek yang tidak diinginkan ini. Penggunaan dioda penjepit eksternal pada input dan output, penghentian yang tepat dari input yang tidak digunakan dan catu daya yang diatur dengan fitur pembatas arus juga membantu meminimalkan kemungkinan terjadinya kondisi latch-up dan meminimalkan efeknya jika itu terjadi.

5.5.2 Subfamili CMOS

5.5.2.1 4000-series

IC CMOS seri 4000A, yang diperkenalkan oleh RCA, adalah yang pertama tiba di tempat kejadian dari Keluarga logika CMOS. Subfamili CMOS 4000A sekarang sudah usang dan telah digantikan oleh 4000B dan subfamili 4000UB. Karena itu kami tidak akan membahasnya secara rinci. Seri 4000B adalah tegangan tinggi versi seri 4000A, dan juga semua output dalam seri ini di-buffer. Seri 4000UB juga merupakan versi tegangan tinggi dari seri 4000A, tetapi di sini keluarannya tidak di-buffer. A buffered

Perangkat CMOS adalah perangkat yang memiliki impedansi keluaran konstan terlepas dari status logika masukannya. Jika kita mengingat skema internal gerbang logika CMOS dasar yang dijelaskan sebelumnya, kita akan melihat bahwa, dengan pengecualian inverter, impedansi keluaran dari gerbang lain bergantung pada status logika dari input. Variasi dalam impedansi keluaran ini terjadi karena kombinasi yang bervariasi dari MOSFET yang melakukan kombinasi input tertentu. Semua perangkat yang di-buffer ditentukan oleh akhiran 'B' dan disebut sebagai seri 4000B. Perangkat seri 4000 yang memenuhi seri 4000B spesifikasi kecuali untuk spesifikasi VIL dan VIH dan bahwa output tidak buffer disebut perangkat tanpa buffer dan dikatakan termasuk dalam seri 4000UB.

Gambar 5.51 dan 5.52 menunjukkan perbandingan antara skema internal dari dua input buffer NOR (Gbr. 5.51) dan NOR dua input tanpa buffer (Gbr. 5.52). Sebuah gerbang buffer telah diterapkan dengan menggunakan inverter pada masukan ke NAND dua masukan yang keluarannya memberi makan inverter lain. Ini adalah pengaturan tipikal yang diikuti oleh berbagai pabrikan, karena inverter pada input meningkat kekebalan kebisingan. Pengaturan lain yang mungkin adalah NOR dua masukan yang keluarannya memberi makan dua inverter yang terhubung seri.

Variasi dalam impedansi keluaran gerbang yang tidak disangga lebih besar untuk gerbang dengan jumlah yang lebih besar masukan. Misalnya, gerbang tanpa buffer memiliki impedansi keluaran 200–400 dalam kasus dua masukan gerbang, 133–400 untuk gerbang tiga masukan dan 100–400 untuk gerbang dengan empat masukan. Memiliki gerbang penyangga impedansi keluaran 400. Karena mereka memiliki impedansi keluaran maksimum yang sama, minimumnya

5.5.2.2 Seri 74C

Subfamili CMOS 74C menawarkan penggantian pin-ke-pin dari fungsi logika TTL 74-series. Untuk Misalnya, jika 7400 adalah quad NAND dua masukan dalam TTL standar, maka 74C00 adalah NAND dua masukan segi empat dengan koneksi pin yang sama di CMOS. Parameter karakteristik CMOS seri 74C adalah kurang lebih sama dengan perangkat seri 4000.

5.5.2.3 Seri 74HC / HCT

Seri 74HC / HCT adalah versi CMOS kecepatan tinggi dari fungsi logika seri 74C. Ini adalah dicapai dengan menggunakan teknologi CMOS gerbang-silikon daripada teknologi CMOS gerbang-logam yang digunakan dalam subfamili CMOS 4000-series sebelumnya. Seri 74HCT hanyalah variasi proses dari seri 74HC. Perangkat seri 74HC / HCT memiliki urutan kecepatan perpindahan yang lebih tinggi dan juga banyak kemampuan drive output yang lebih tinggi daripada perangkat seri 74C. Seri ini juga menawarkan penggantian pin-to-pin dari 74-seri fungsi logika TTL. Selain itu, perangkat seri 74HCT memiliki input yang kompatibel dengan TTL.

5.5.2.4 Seri 74AC / ACT

Seri 74AC saat ini merupakan keluarga logika CMOS tercepat. Keluarga logika ini memiliki yang terbaik kombinasi kecepatan tinggi, konsumsi daya rendah, dan kemampuan penggerak output tinggi. Sekali lagi, 74ACT hanya variasi proses 74AC. Selain itu, perangkat seri 74ACT memiliki kompatibel dengan TTL masukan.

- Resistor

Resistor adalah komponen elektronika pasif yang memiliki nilai resistansi atau hambatan tertentu yang berfungsi untuk membatasi dan mengatur arus listrik dalam suatu rangkaian elektronika. Satuan Resistor adalah Ohm (simbol: Ω) yang merupakan satuan SI untuk resistansi listrik. Resitor mempunyai nilai resistansi (tahanan) tertentu yang dapat memproduksi tegangan listrik di antara kedua pin dimana nilai tegangan terhadap resistansi tersebut berbanding lurus dengan arus yang mengalir, berdasarkan persamaan hukum Ohm (V = I.R ).

- Gerbang NOT

Gerbang NOT disebut juga inverter, gerbang ini hanya mempunyai satu input dan satu output. Persamaan logika aljabar Boole untuk output gerbang NOT adalah Y = Ā . Jadi output gerbang NOT selalu merupakan kebalikan dari input-nya. Jika input diberikan logika tinggi maka pada output akan dihasilkan logika rendah, dan pada saat input diberikan logika rendah maka pada output akan dihasilkan logika tinggi (Tokheim, 1995). Simbol gerbang NOT diperlihatkan pada Gambar 2.1 dan tabel kebenaran gerbang NOT diperlihatkan pada Tabel 2.1.

- Gerbang XOR

Simbol dari gerbang Eksklusif OR (XOR) dengan 2 variabel input dan satu buah output diperlihatkan pada Gambar 2.7. Tabel kebenarannya dapat dilihat pada Tabel 2.7. Dari tabel kebenaran XOR, dapat dilihat bahwa output pada logik 1 jika salah satu input pada keadaan logik 0 atau logik 1, sedangkan output pada keadaan logik 0 apabila kedua logik input sama. (Tokheim, 1995).

- Gerbang AND

Gerbang AND adalah gerbang logika yang terdiri dari dua atau lebih input dan hanya memiliki satu output. Output gerbang AND akan tinggi hanya jika semua input tinggi, dan jika salah satu atau lebih input berlogika rendah maka output akan rendah. Persamaan logika aljabar Boole gerbang AND adalah Y=A.B. Pada Aljabar Boole operasi gerbang AND diberi tanda ”kali” atau tanda ”titik” (Malvino, 1983). Simbol gerbang AND ditunjukkan pada Gambar 2.3. Tabel kebenaran diperlihatkan pada Tabel 2.3.

- Gerbang OR

Gerbang OR adalah gerbang logika dasar yang mempunyai dua atau lebih input dan hanya memiliki satu output. Output gerbang OR akan berlogika tinggi apabila salah satu atau lebih input ada yang berlogika tinggi, dan output akan berlogika rendah hanya pada saat seluruh input berlogika rendah. Persamaan logika aljabar Boole untuk output gerbang OR adalah Y=A+B. Pada aljabar Boole operasi gerbang OR diberi tanda ”tambah” (Malvino, 1983). Simbol gerbang OR ini ditunjukkan pada Gambar 2.4 dan tabel kebenaran gerbang OR diperlihatkan Tabel 2.4.

- Gerbang NAND

Gerbang NAND merupakan gabungan dari gerbang AND dan NOT. Output gerbang NAND selalu merupakan kebalikan dari output gerbang AND untuk input yang sama. Jadi output akan berlogika tinggi jika salah satu atau lebih input-nya berlogika rendah, dan output akan berlogika rendah hanya pada saat semua input-nya berlogika tinggi. (Tokheim, 1995). Simbol gerbang NAND ini ditunjukkan pada Gambar 2.5. Tabel kebenaran gerbang NAND diperlihatkan pada Tabel 2.5.

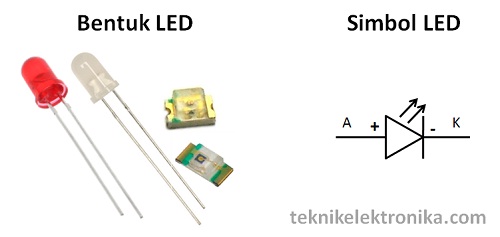

- LED

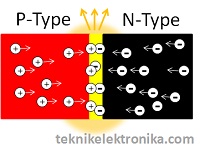

LED merupakan keluarga dari Dioda yang terbuat dari Semikonduktor. Cara kerjanya pun hampir sama dengan Dioda yang memiliki dua kutub yaitu kutub Positif (P) dan Kutub Negatif (N). LED hanya akan memancarkan cahaya apabila dialiri tegangan maju (bias forward) dari Anoda menuju ke Katoda.

Ketika LED dialiri tegangan maju atau bias forward yaitu dari Anoda (P) menuju ke Katoda (K), Kelebihan Elektron pada N-Type material akan berpindah ke wilayah yang kelebihan Hole (lubang) yaitu wilayah yang bermuatan positif (P-Type material). Saat Elektron berjumpa dengan Hole akan melepaskan photon dan memancarkan cahaya monokromatik (satu warna).

Tegangan Maju LED

- Logicstate

Logicstate yaitu pengertian logis, benar atau salah, dari sinyal biner yang diberikan. Sinyal biner adalah sinyal digital yang hanya memiliki dua nilai yang valid. Dalam istilah fisik, pengertian logis dari sinyal biner ditentukan oleh level tegangan atau nilai arus sinyal, dan ini pada gilirannya ditentukan oleh teknologi perangkat. Dalam sirkuit TTL, misalnya, keadaan sebenarnya diwakili oleh logika 1, kira-kira sama dengan +5 volt pada garis sinyal; logika 0 kira-kira 0 volt. Tingkat tegangan antara 0 dan +5 volt dianggap tidak ditentukan.Karena hanya dua status logika, logika 1 dan logika 0, yang dimungkinkan, teknik aljabar Boolean dapat digunakan untuk menganalisis rangkaian digital yang melibatkan sinyal biner. Istilah logika positif diterapkan ke sirkuit di mana logika 1 ditetapkan ke level tegangan yang lebih tinggi; Dalam rangkaian logika negatif, logika 1 ditunjukkan dengan level tegangan yang lebih rendah.

4. PROSEDUR PERCOBAAN [KEMBALI]

1) Buka aplikasi proteus

2) Pilih komponen yang dibutuhkan.

3) Rangkai setiap komponen menjadi rangkaian yang diinginkan

4) Ubah spesifikasi komponen sesuai kebutuhan

5) Jalankan simulasi rangkaian.

5. RANGKAIAN SIMULASI [KEMBALI]

6. VIDEO [KEMBALI]

7. SOAL [KEMBALI]

Example :

1. Gambarkan skema internal: (a) fungsi logika AND-OR-INVERT dua-lebar, empat-masukan di CMOS dan (b) fungsi logika dua lebar, empat masukan OR-DAN-INVERT di CMOS.

Jawab :

(a) Mari kita asumsikan bahwa A, B, C, D, E, F, G dan H adalah variabel logika. Output Y dari logika fungsi kemudian dapat diekspresikan oleh persamaan

Mengikuti prinsip-prinsip yang dijelaskan sebelumnya dalam teks, skema internal ditunjukkan pada Gambar 5.53 (a). Koneksi seri MOSFET saluran-N di sebelah kiri mensimulasikan ANDing dari A, B, C dan D, sedangkan koneksi seri MOSFET saluran-N di sebelah kanan mensimulasikan ANDing dari E, F, G dan H. Hubungan paralel dari dua cabang menghasilkan ORing dari output ANDed. Sejak Susunan MOSFET kanal-P merupakan pelengkap dari susunan MOSFET kanal-N, hasil akhir adalah apa yang diberikan oleh Persamaan (5.5).

(b) Keluaran Y dari fungsi logika ini dapat diekspresikan dengan persamaan

Gambar 5.53 (b) menunjukkan skema internal, yang dapat dijelaskan pada baris yang sama.

2. Tentukan fungsi logika yang dilakukan oleh sirkuit digital CMOS pada Gambar 5.54

Jawab :Sirkuit yang diberikan dapat dibagi menjadi dua tahap. Tahap pertama terdiri dari dua buah inverter yang menghasilkan Ā dan Б. Tahap kedua adalah rangkaian AND-OR-INVERT dua-lebar, dua-masukan. Masukan ke yang pertama AND adalah Ā dan B, dan masukan ke AND kedua adalah A dan Б. Oleh karena itu, keluaran akhir diberikan oleh

Problem :

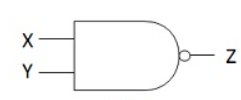

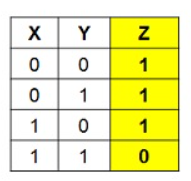

1. Buatlah tabel kebenaran gerbang di bawah ini!

Jawab :

2. Buatlah berbagai simbol dari complementary gate!

Jawab :

Pilihan Ganda :

8. DOWNLOAD FILE [KEMBALI]

Tidak ada komentar:

Posting Komentar