1. TUJUAN [KEMBALI]

penulisan blog ini bertujuan untuk :

· Dapat membuat dan mensimulasikan spesial output gates.

· Dapat memahami teori dan prinsip kerja dari spesial output gates.

2. ALAT DAN BAHAN [KEMBALI]

ALAT :

1. Power Supply

2. Osiloskop

BAHAN :

1. Resistor

Komponen Input :

Komponen Output :

Komponen Lainnya :

3. DASAR TEORI [KEMBALI]

- Ringkasan

10.10 Flip-Flop Applications

Flip-flop digunakan dalam berbagai rangkaian aplikasi, yang paling umum di antaranya adalah rangkaian pembagian frekuensi dan penghitungan serta rangkaian penyimpanan dan transfer data. Area aplikasi ini dibahas panjang lebar di Bab 11 tentang penghitung dan register. Kedua aplikasi ini menggunakan susunan sandal jepit bertingkat dengan atau tanpa beberapa logika kombinasional tambahan untuk menjalankan fungsi yang diinginkan. Penghitung dan register tersedia dalam bentuk IC untuk berbagai aplikasi rangkaian digital. Aplikasi lain dari sandal jepit termasuk penggunaannya untuk sakelar debouncing, di mana bahkan flip-flop yang tidak di-clock (seperti kait NAND atau NOR) dapat digunakan, untuk menyinkronkan input asinkron dengan input jam dan untuk identifikasi tepi input sinkron . Ini secara singkat dijelaskan dalam paragraf berikut.

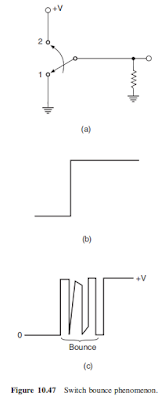

10.10.1 Switch Debouncing

Karena fenomena pantulan sakelar, sakelar mekanis tidak dapat digunakan sedemikian rupa untuk menghasilkan transisi tegangan yang bersih. Lihat Gambar 10.47 (a). Ketika sakelar dipindahkan dari posisi 1 ke posisi 2, yang diinginkan pada output adalah transisi tegangan bersih dari 0 ke + V volt, seperti yang ditunjukkan pada Gambar 10.47 (b). Apa yang sebenarnya terjadi ditunjukkan pada Gambar 10.47 ( c). Output membuat beberapa transisi antara 0 dan + V volt selama beberapa milidetik karena kontak pantulan sebelum akhirnya menetap di + V. volt. Demikian pula, ketika dipindahkan dari posisi 2 kembali ke posisi 1, ia membuat beberapa transisi sebelum berhenti pada 0 V. Meskipun perilaku acak ini hanya berlangsung selama beberapa milidetik, perilaku acak ini tidak dapat diterima untuk banyak aplikasi rangkaian digital. NAND atau kait NOR dapat mengatasi masalah ini dan memberikan transisi keluaran yang bersih. Gambar 10.48 menunjukkan rangkaian pantulan sakelar tipikal yang dibangun di sekitar kait NAND. Rangkaian berfungsi sebagai berikut.

Saat sakelar berada di posisi 1, output berada pada level '0'. Ketika dipindahkan ke posisi 2, output pergi ke level '1' dalam beberapa nanodetik (tergantung pada penundaan propagasi gerbang NAND) setelah kontak pertama dengan posisi 2. Saat kontak sakelar memantul, itu membuat dan putus kontak dengan posisi 2 sebelum akhirnya menetap di posisi yang diinginkan. Pembuatan kontak selalu mengarah ke level '1' pada output, dan putusnya kontak juga mengarah ke level '1' pada output karena fakta bahwa pemutusan kontak menghasilkan level '1' pada kedua input kait yang memaksa keluaran untuk menahan keadaan logika yang ada. Fakta bahwa ketika sakelar dibawa kembali ke posisi 1, output membuat transisi yang rapi ke level '0' dapat dijelaskan pada baris yang sama.

10.10.2 Flip-Flop Synchronization

Pertimbangkan situasi di mana input jam tertentu, yang bekerja dalam hubungannya dengan berbagai input sinkron, akan di-gated dengan pulsa gating yang dibangkitkan secara tidak sinkron, seperti yang ditunjukkan pada Gambar 10.49. Output dalam hal ini memiliki pulsa clock di salah satu atau kedua ujungnya diperpendek lebarnya, seperti yang ditunjukkan pada Gambar 10.49. Masalah ini dapat diatasi dan operasi gating disinkronkan dengan bantuan flip-flop, seperti yang ditunjukkan pada Gambar 10.50.

10.10.3 Detecting the Sequence of Edges

Flip-flops juga dapat digunakan untuk mendeteksi urutan kemunculan tepi naik dan turun. Gambar 10.51 menunjukkan bagaimana flip-flop dapat digunakan untuk mendeteksi apakah tepi positif A mengikuti atau mendahului tepi positif lainnya B. Kedua tepi tersebut masing-masing diterapkan ke input D dan clock input dari flip- D yang dipicu tepi positif flip-flop. Jika tepi A tiba lebih dulu, kemudian, saat tepi B tiba, keluarannya berubah dari 0 ke 1. Jika sebaliknya, ia tetap pada tingkat '0'.

- Resistor

Resistor adalah komponen elektronika pasif yang memiliki nilai resistansi atau hambatan tertentu yang berfungsi untuk membatasi dan mengatur arus listrik dalam suatu rangkaian elektronika. Satuan Resistor adalah Ohm (simbol: Ω) yang merupakan satuan SI untuk resistansi listrik. Resitor mempunyai nilai resistansi (tahanan) tertentu yang dapat memproduksi tegangan listrik di antara kedua pin dimana nilai tegangan terhadap resistansi tersebut berbanding lurus dengan arus yang mengalir, berdasarkan persamaan hukum Ohm (V = I.R ).

- Gerbang NOT

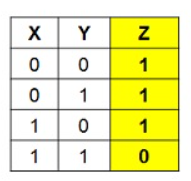

Gerbang NOT disebut juga inverter, gerbang ini hanya mempunyai satu input dan satu output. Persamaan logika aljabar Boole untuk output gerbang NOT adalah Y = Ā . Jadi output gerbang NOT selalu merupakan kebalikan dari input-nya. Jika input diberikan logika tinggi maka pada output akan dihasilkan logika rendah, dan pada saat input diberikan logika rendah maka pada output akan dihasilkan logika tinggi (Tokheim, 1995). Simbol gerbang NOT diperlihatkan pada Gambar 2.1 dan tabel kebenaran gerbang NOT diperlihatkan pada Tabel 2.1.

- Gerbang XOR

Simbol dari gerbang Eksklusif OR (XOR) dengan 2 variabel input dan satu buah output diperlihatkan pada Gambar 2.7. Tabel kebenarannya dapat dilihat pada Tabel 2.7. Dari tabel kebenaran XOR, dapat dilihat bahwa output pada logik 1 jika salah satu input pada keadaan logik 0 atau logik 1, sedangkan output pada keadaan logik 0 apabila kedua logik input sama. (Tokheim, 1995).

- Gerbang AND

Gerbang AND adalah gerbang logika yang terdiri dari dua atau lebih input dan hanya memiliki satu output. Output gerbang AND akan tinggi hanya jika semua input tinggi, dan jika salah satu atau lebih input berlogika rendah maka output akan rendah. Persamaan logika aljabar Boole gerbang AND adalah Y=A.B. Pada Aljabar Boole operasi gerbang AND diberi tanda ”kali” atau tanda ”titik” (Malvino, 1983). Simbol gerbang AND ditunjukkan pada Gambar 2.3. Tabel kebenaran diperlihatkan pada Tabel 2.3.

- Gerbang OR

Gerbang OR adalah gerbang logika dasar yang mempunyai dua atau lebih input dan hanya memiliki satu output. Output gerbang OR akan berlogika tinggi apabila salah satu atau lebih input ada yang berlogika tinggi, dan output akan berlogika rendah hanya pada saat seluruh input berlogika rendah. Persamaan logika aljabar Boole untuk output gerbang OR adalah Y=A+B. Pada aljabar Boole operasi gerbang OR diberi tanda ”tambah” (Malvino, 1983). Simbol gerbang OR ini ditunjukkan pada Gambar 2.4 dan tabel kebenaran gerbang OR diperlihatkan Tabel 2.4.

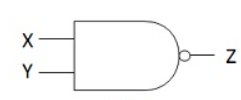

- Gerbang NAND

Gerbang NAND merupakan gabungan dari gerbang AND dan NOT. Output gerbang NAND selalu merupakan kebalikan dari output gerbang AND untuk input yang sama. Jadi output akan berlogika tinggi jika salah satu atau lebih input-nya berlogika rendah, dan output akan berlogika rendah hanya pada saat semua input-nya berlogika tinggi. (Tokheim, 1995). Simbol gerbang NAND ini ditunjukkan pada Gambar 2.5. Tabel kebenaran gerbang NAND diperlihatkan pada Tabel 2.5.

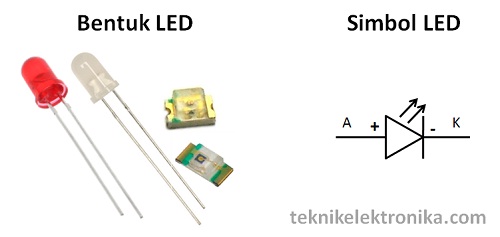

- LED

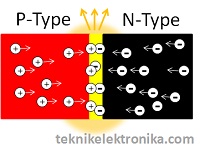

LED merupakan keluarga dari Dioda yang terbuat dari Semikonduktor. Cara kerjanya pun hampir sama dengan Dioda yang memiliki dua kutub yaitu kutub Positif (P) dan Kutub Negatif (N). LED hanya akan memancarkan cahaya apabila dialiri tegangan maju (bias forward) dari Anoda menuju ke Katoda.

Ketika LED dialiri tegangan maju atau bias forward yaitu dari Anoda (P) menuju ke Katoda (K), Kelebihan Elektron pada N-Type material akan berpindah ke wilayah yang kelebihan Hole (lubang) yaitu wilayah yang bermuatan positif (P-Type material). Saat Elektron berjumpa dengan Hole akan melepaskan photon dan memancarkan cahaya monokromatik (satu warna).

Tegangan Maju LED

- Logicstate

Logicstate yaitu pengertian logis, benar atau salah, dari sinyal biner yang diberikan. Sinyal biner adalah sinyal digital yang hanya memiliki dua nilai yang valid. Dalam istilah fisik, pengertian logis dari sinyal biner ditentukan oleh level tegangan atau nilai arus sinyal, dan ini pada gilirannya ditentukan oleh teknologi perangkat. Dalam sirkuit TTL, misalnya, keadaan sebenarnya diwakili oleh logika 1, kira-kira sama dengan +5 volt pada garis sinyal; logika 0 kira-kira 0 volt. Tingkat tegangan antara 0 dan +5 volt dianggap tidak ditentukan.Karena hanya dua status logika, logika 1 dan logika 0, yang dimungkinkan, teknik aljabar Boolean dapat digunakan untuk menganalisis rangkaian digital yang melibatkan sinyal biner. Istilah logika positif diterapkan ke sirkuit di mana logika 1 ditetapkan ke level tegangan yang lebih tinggi; Dalam rangkaian logika negatif, logika 1 ditunjukkan dengan level tegangan yang lebih rendah.

4. PROSEDUR PERCOBAAN [KEMBALI]

1) Buka aplikasi proteus

2) Pilih komponen yang dibutuhkan.

3) Rangkai setiap komponen menjadi rangkaian yang diinginkan

4) Ubah spesifikasi komponen sesuai kebutuhan

5) Jalankan simulasi rangkaian.

5. RANGKAIAN SIMULASI [KEMBALI]

6. VIDEO [KEMBALI]

7. SOAL [KEMBALI]

Example :

Example 10.7

Gambar 10.52 menunjukkan dua bentuk gelombang berpulsa A dan B, dengan bentuk gelombang A memimpin bentuk gelombang B dalam fase, seperti yang ditunjukkan pada gambar. Sarankan rangkaian flip-flop untuk mendeteksi kondisi ini dengan menghasilkan (a) keluaran Q logika '1' dan (b) keluaran Q logika '0'.

Jawab :

(a) Flip-flop D yang dipicu tepi positif, seperti yang ditunjukkan pada Gambar 10.53 (a), dapat digunakan untuk tujuan tersebut. Bentuk gelombang A diterapkan ke masukan D, dan bentuk gelombang B diterapkan ke masukan clock. Jika kita memeriksa dua bentuk gelombang, kita akan menemukan bahwa, pada setiap kemunculan tepi depan bentuk gelombang B, bentuk gelombang A berada dalam keadaan logika '1'. Jadi, keluaran Q dalam hal ini akan selalu dalam keadaan logika '1'.

(b) Dengan menukar koneksi bentuk gelombang A dan B seperti yang ditunjukkan pada Gambar 10.53 (b), keluaran Q akan berada dalam keadaan logika '0' selama bentuk gelombang A mengarah pada bentuk gelombang B dalam fase. Dalam hal ini, pada setiap kemunculan tepi depan bentuk gelombang A (masukan clock), bentuk gelombang B (masukan D) berada dalam keadaan logika '0'.

Problem :

1. Buatlah tabel kebenaran gerbang di bawah ini!

Jawab :

2. Buatlah berbagai simbol dari complementary gate!

Jawab :

Pilihan Ganda :

8. DOWNLOAD FILE [KEMBALI]

Tidak ada komentar:

Posting Komentar